历经多年的发展和沉淀,半导体芯片封装技术在市场研发中已经越来越成熟,如今已有数百种封装类型。而在这数百种封装类型中,扇出型封装技术日益火热起来,其更被认为是延续和超越摩尔定律的关键技术方案。微距追赶时代,中科智芯的先进封装技术——扇出封装凭借其在产品良率、可靠性、制造成本、规模化量产速度等优势,得到了市场的广泛认可。

在这里,我们将向大家介绍扇出封装技术的优势和关键工艺。

一、扇出封装技术优势

自2000年以来,晶圆级封装WLP已被广泛采用并投入生产,其中大部分封装和测试都是以完整的晶圆形式完成的。WLP不需要中间集成电路(IC)基板,因此可以被更薄的封装外形所容纳,并且可以直接安装到主板上。扇出封装(FO)特有的是互连超越芯片边缘,支持多芯片、2.5D和3D封装解决方案。FO技术可用于制造再分布层(RDL)转接板,这是2.5D封装的低成本替代方案。此外,FO技术有助于垂直方向的多芯片堆叠,从而实现3D封装解决方案。输入/输出(IO)密度可伸缩性极为灵活,还具有通过2D、2.5D和3D结构将无源和有源芯片集成在同一个封装中的这些优势和极大的小型化潜力,使其成为半导体封装的首选技术之一。

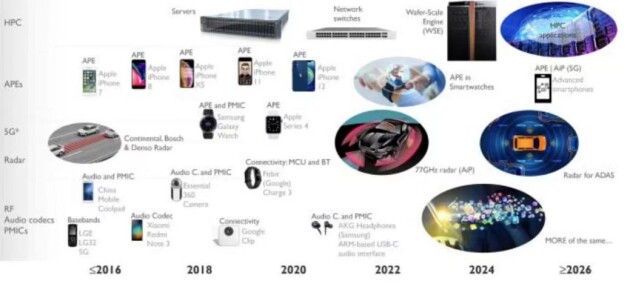

FO-WLP是一种多功能半导体封装技术,可用于各种关键应用,如分离式大型处理器芯片、移动APE、汽车雷达和RF、音频编解码器、PMIC和潜在的5G封装天线(AiP)。与传统的fiip芯片相比,它具有更薄的封装尺寸、更高的RF性能、更高的I/O密度和更低的热阻等优点。除了扇出电气I/O外,它还可用于各种2.5D和3D多芯片集成。今天,FO-WLP已经从低端封装技术发展成为高性能、高性价比的集成平台,如图1所示。

图1扇出封装市场驱动因素路线图

扇出封装的趋势是走向更多的集成,而FO-WLP是未来扩展到异构集成的潜在候选。这为新的MCMs(多芯片模块)、PoPs(层叠封装)和sip提供了可实施性。FO-WLP的与众不同在于能够嵌入多种芯片(独立于芯片类型、尺寸或侧面),允许多种集成可能性:小芯片、大芯片、堆叠或并排多芯片;单芯片和多芯片配置的2D解决方案;2.5D转接板解决方案;3D SiP和PoP解决方案,可包括面对面(有源芯片正面对芯片背面)或面对面(有源芯片正面对有源芯片正面或F2F)选项;或者与无源和有源组件的异构集成。

FO封装技术正在渗透更高端的I/O密度,远远超过每平方毫米18个,以及更精细的RDL,L/S测量值远低于5微米/5 μm。TSMC和日月光分别以其FO on substrate technology InFO_oS和FoCoS投入生产,用于网络应用。未来五年,封装尺寸将超过25 mm × 25 mm,L/S将走向2微米/2微米及以下。rdl的数量将增加到4个及以上,封装厚度(不含BGA)将达到150μm。

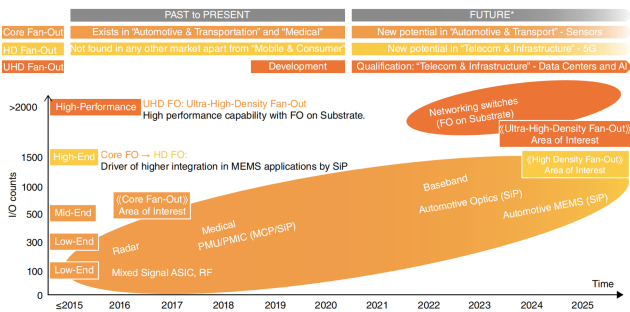

随着技术的进步(更高的I/O数、RDL数、TMV、芯片持续等),集成度更高的FO架构(如PoP和SiP)将会被广泛应用。)。不同终端应用的FO技术路线图如图2所示。

图2 不同终端应用的FO技术路线图

二、扇出封装关键工艺

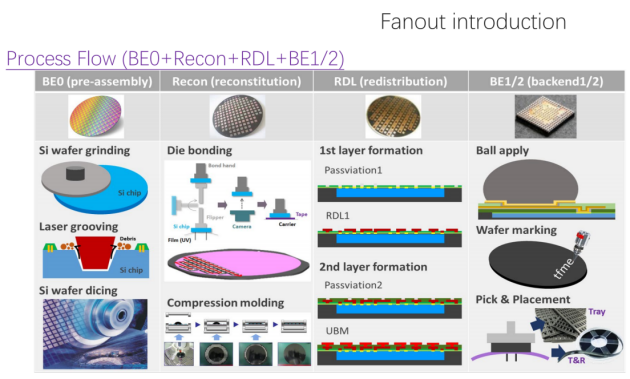

扇出封装技术在不同的OSAT形成各自的技术平台,归纳起来主要有三种做法:die first/face up,die first/face down和RDL first。以业内技术较成熟、市场应用较广的eWLB扇出技术为例,其工艺路线如下图3。

图3 eWLB工艺流程

eWLB工艺流程分为以下三大部分:

1、Re-con(晶圆重构 wafer reconstitution):将来料晶圆通过研磨、划片分割成单独的芯粒,再将这些芯粒贴合拼在同一个金属载板上后,通过塑封的方式将这些晶粒重新构成一片EMC晶圆;

2、RDL(再布线):在重构的EMC晶圆上通过金属薄膜溅射、光刻、电镀、去胶、刻蚀等工艺实现芯片内电路的再分布;

3、封装成型(Backend):在芯粒再布线形成的焊盘上植入焊球完成芯片的电路连接,然后将封装好的package通过刀片分割成一个单独的实体后包装出货。

近年来,中科智芯一直坚持创新,在先进封装技术领域内厚积薄发,不断夯实在行业发展地位。芯片制造工艺的发展不会停滞,无论是现在还是未来,中科智芯都将精准把握市场趋势、紧扣科技脉搏,为推动芯片封装技术的发展贡献力量。